Everspin Embedded MRAM

2016-09-02 10:07:34

The Need for Embedded MRAM (eMRAM)

Today's embedded products implement complex memory systems to enable Data Integrity, Reliability, and Low Energy. This is due to the fact that current mainstream memories are limited in speed, power, and endurance (Flash, EEPROM) or cannot retain data without power (SRAM, DRAM). In addition, current mainstream memory is approaching limits as to how small current mainstream memory technology can scale. Therefore the market is looking to Emerging Memory to solve the technology limitations, and Everspin is leading the effort.

Everspin Embedded MRAM is deployed today.

Everspin has significant experience in enabling silicon suppliers with eMRAM. In fact, roughly half of Everspin's total unit volume is embedded, and the applications range from consumer to aerospace. Our MRAM technology and proprietary IP enables us to provide non-volatile, fast-write embedded memory blocks that are compatible with CMOS Logic designs, targeted for 180nm and 130nm CMOS processes (for field-switched eMRAM), as well as 40nm and 28nm CMOS processes (for perpendicular-MTJ Spin Torque eMRAM).

Everspin's eMRAM as the next Mainstream Embedded Memory

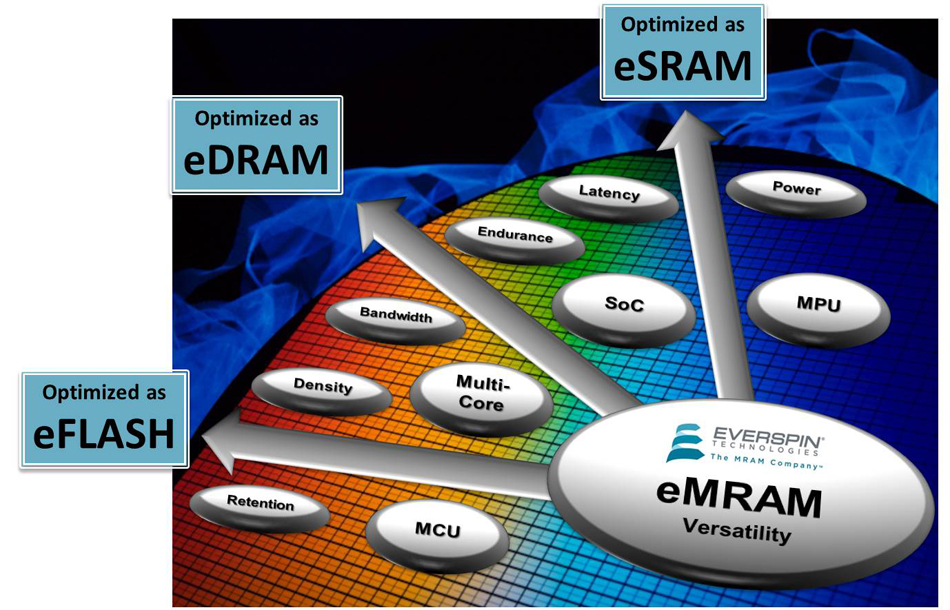

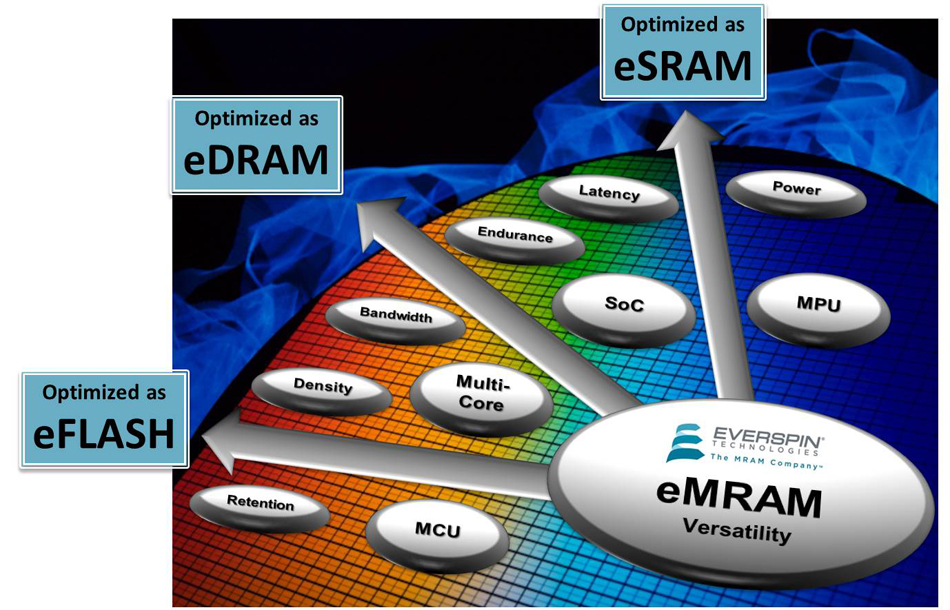

Compared to other current and emerging memory technologies, implementing eMRAM is relatively simple. For one, Everspin MRAM and ST-MRAM technology is implemented in the final metal layers of standard CMOS process. Also, MRAM and ST-MRAM is "base technology independent", meaning that a standard MRAM MTJ (such as a perpendicular MTJ in 28nm) can be applied to almost any base CMOS process (65nm, 40nm, 28nm, etc). Finally, the technology is highly scalable and versatile, allowing eMRAM to dominate over multiple embedded memory types, such as Flash, DRAM, and/or SRAM through bit cell design optimization.